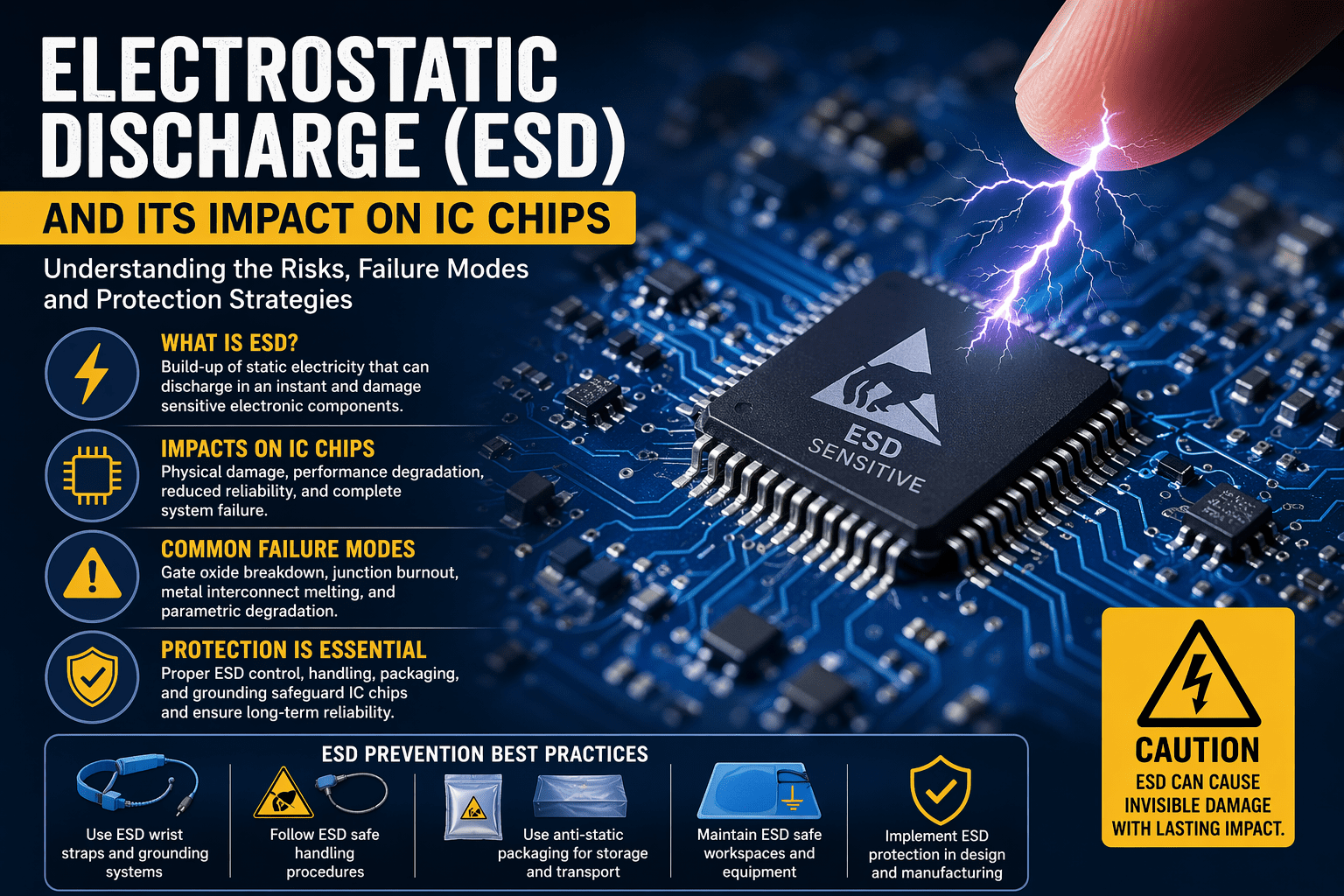

The Impact of Electrostatic Discharge on Sensitive Electronic Components

- 1 Generation of Static Electricity

- 2 Impacts caused by ESD on Electronic Components

- 2.1 3.1 Physical Damage

- 2.2 3.2 Performance Degradation

- 2.3 3.3 Reduced Reliability

- 2.4 3.4 Common ESD Stress Conditions for Real Applications

- 3 Damage Mechanisms of Electrostatic Discharge

- 3.1 4.1 Thermal Effects

- 3.2 4.2 Electrical Effects

- 3.3 4.3 Mechanical Effects

- 3.4 3.4 Typical ESD Failure Modes for Inclined Chip

- 3.4.1 Gate Oxide Breakdown

- 3.4.2 Junction Burnout

- 3.4.3 Metal Interconnect Melting

- 3.4.4 Latent ESD Damage

- 4 Prevention and Protection Measures

- 4.1 5.1 ESD Control Programs

- 4.2 5.2 Grounding and Shielding

- 4.3 5.3 Humidity Control

- 4.4 5.4 ESD Protection Devices

- 5 Conclusion

Electrostatic discharge (ESD) is a ubiquitous but very dangerous phenomenon in the electronics industry. It can be produced due to human movement, equipment operation, or environmental conditions. A region of concern that has the most salient effects on electronic components is electrostatic discharge, particularly as electronic technology moves towards higher levels of integration with smaller geometries and lower operating voltages.

As the size of IC chips, microprocessors, memory devices, and sensors is very small in area with a thin insulating layer, these sensitive electronic components are highly susceptible to electrostatic discharge (ESD) events. A single electrostatic discharge event could irreversibly damage an IC chip, thereby compromising the performance, reliability, and useful life of the entire electronic system.

Generation of Static Electricity

Electric charge generated is the electricity that relies on static, the buildup of electric charge on the surface of objects. Dry environments allow the frictional force between the human body and garment to be extremely high, along with the repeated contact and separation of the material used on equipment during operation.

Electronic manufacturing and/or assembly processes, those normally utilize insulating materials like plastics and rubbers. These materials inhibit the rapid dissipation of charges, which increases the risk of ESD. Consequently, electrostatic risks are a constant threat to the integrity of IC chips and other electronic components during production, testing, storage, and transportation.

Impacts caused by ESD on Electronic Components

Electrostatic discharge can generate extremely high voltage and current in a very short time, which causes many different kinds of damage to electronic devices, especially IC chips.

3.1 Physical Damage

High-voltage ESD sweeps away gate oxides, PN junctions, or metal interconnects within an IC chip, eventually melting burnings or causing permanent dielectric breakdown. Such damage is permanent and one of the most serious ESD effects on IC chips.

3.2 Performance Degradation

Even when ESD does not cause instantaneous physical failure, the performance of a device is degraded. To illustrate, memory ICs may lose data; analog IC chips may show parameter drift, and sensor ICs may become less sensitive. Such cases show yet another way electrostatic discharge compromises the integrated circuit in a subtly malevolent manner.

3.3 Reduced Reliability

Long-term reliability of chips is greatly affected if damage from either subtle or chronic ESD has occurred. ESD-induced failures in IC chips can cause serious operational risks in applications that require high stability (such as industrial automation, medical electronics, and aerospace systems).

3.4 Common ESD Stress Conditions for Real Applications

IC chip is defective in the SMT printed circuit assembly lines

The ESD can be introduced to IC chips easily due to poor grounding or defective ESD control during high-speed SMT placement, inspection, or manual handling.

Improper packaging during storage and transport can lead to ESD failures.

Without anti-static packaging, IC chips and electronic components can build up charge due to friction and environmental conditions, which may not be apparent until they get into the hands of end users, resulting in concealed ESD failure.

The known ESD failure modes for industrial control systems and medical devices.

Due to ESD-induced latent defects in IC chip may be intermittent failure, safety, and system reliability issues for mission-critical systems.

Damage Mechanisms of Electrostatic Discharge

4.1 Thermal Effects

The instant energy emission in an ESD event can create extreme localized temperature, which is harmful to semiconductor material and internal structures inside IC chips.

4.2 Electrical Effects

The temporary high current resulting from ESD could go above the electrical tolerance of an integrated circuit and lead to dielectric breakdown or junction failure.

4.3 Mechanical Effects

High electric fields of electrostatic discharge are capable of causing mechanical stress within the IC chip, resulting in micro-cracking or broken interconnects.

3.4 Typical ESD Failure Modes for Inclined Chip

Electrostatic discharge can potentially harm IC chips in several forms, depending on the energy of discharge, device structure, and fabrication technology. Knowledge of the well-known ESD failure modes is important in determining field failures and effective ESD protection for integrated circuits.

Gate Oxide Breakdown

Gate oxide breakdown is one of the most frequent and serious ESD failure modes in current integrated circuit (IC) chips; this scenario mainly affects complementary metal–oxide–semiconductor (CMOS)-based devices. In advanced semiconductor processes, the oxide layers of devices are very thin, so that even a short ESD pulse will exceed the dielectric strength of the gate oxide.

Breakdown causes the IC chip to leak more current, malfunction, or even lose function completely. Often, gate oxide damage creates latent ESD defects that become apparent only after a long time in operation.

Junction Burnout

The term junction burnout refers to the phenomenon when the high current caused during an ESD event flows through PN junctions inside an IC chip. The localized heating causes irreparable damage at junction regions, which in turn leads to unwanted electrical performance and even complete failure.

Such a failure mode is more often seen in high current density power IC chips and analog integrated circuits.

Metal Interconnect Melting

When high voltage, necessitating a surge of energy through the thin metal interconnects within an integrated circuit, is released as electrostatic discharge, too much current is forced through to be safely managed. This can lead to localized melting or open-circuit failure if the current exceeds thermal limits of the metal lines.

Metal interconnect damage is one of the most catastrophic failure mechanisms associated with ESD, and almost all IC chips testing done in the lab uses a non-destructive way for testing against this lethal, fast-acting culprit.

Latent ESD Damage

Hidden defects caused by electrostatic discharge that will not actually trigger immediate failure are termed latent ESD damage. Instead, the IC chip itself still functions, but with internal structures that have been weakened.

Eventually, latent defects can become functional failures due to thermal stress, electrical cycling, or environmental factors when the device has been in operation for some time. This latent ESD damage is especially lethal because it reduces the reliability of IC chips dramatically yet goes undetected during routine electrical tests.

Prevention and Protection Measures

Manufacturers and engineers adopt systematic electronic component ESD protection methods (especially for IC chips) in order to reduce the risk derived from ESD.

5.1 ESD Control Programs

Implementing and enforcing ESD control procedures — such as utilizing anti-static clothing, wrist straps, grounded work stations, and ESD-safe packaging — is critical to protecting IC chips.

5.2 Grounding and Shielding

Grounding of equipment, tools, and personnel prevents the charging up of static electricity. ESD exposure to sensitive IC components can be additionally mitigated by shielding materials.

5.3 Humidity Control

Controlling the humidity that ranges from 40% to 60%, in this range, lower ESD will be generated on the objects; therefore, static electricity risk for IC chips has a solution.

5.4 ESD Protection Devices

ESD Protection Components, such as Transient Voltage Suppressors (TVS) or Metal Oxide Varistors (MOVs), protect IC Chips and integrated circuits by absorbing transient energy and preventing electrostatic discharge damage that would otherwise interfere with proper operation.

Conclusion

Applying this effect, its effects on delicate electronic components can result in immediate physical failure or malfunction (e.g., component burn-out), permanent electrical or mechanical breakdown in the long term, and/or a decrease in reliability over time. With these ever-shrinking IC chip geometries and increased integration levels, ESD risks are heightened.

If deemed relevant, using complete ESD protection approaches in addition to following industry standards could help cut down on ESD-related failures, increase IC chip reliability, and prolong the longevity of electronic items.